探秘芯片誕生記 集成電路設(shè)計全流程科普

集成電路(Integrated Circuit, IC),常被稱為芯片,是現(xiàn)代電子設(shè)備的心臟。從智能手機到航天器,無處不在的芯片背后,是一套精密而復(fù)雜的設(shè)計流程。今天,我們就來一起揭開集成電路設(shè)計的神秘面紗,看看一顆芯片是如何從概念走向現(xiàn)實的。

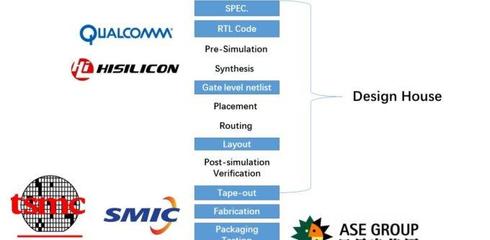

集成電路設(shè)計,通常稱為IC設(shè)計,是一個將系統(tǒng)、邏輯與性能要求轉(zhuǎn)化為具體物理版圖的過程,最終交付給芯片制造廠(Foundry)進行生產(chǎn)。整個流程可以被形象地比喻為建造一座超微型、結(jié)構(gòu)極其復(fù)雜的“城市”。這個過程主要分為前端設(shè)計和后端設(shè)計兩大階段,并遵循著從抽象到具體、從功能到物理的實現(xiàn)路徑。

第一階段:前端設(shè)計——定義芯片的“靈魂”與“大腦”

前端設(shè)計關(guān)注芯片的功能、架構(gòu)和邏輯,核心目標是產(chǎn)出芯片的“電路原理圖”。

- 系統(tǒng)規(guī)格定義:這是設(shè)計的起點。工程師需要明確芯片的用途、性能指標(如速度、功耗)、成本目標以及需要符合的行業(yè)標準。這相當于為整個項目制定一份詳盡的“需求說明書”。

- 架構(gòu)設(shè)計:基于規(guī)格,設(shè)計團隊規(guī)劃芯片的整體架構(gòu)。這包括決定使用哪些核心模塊(如CPU核、GPU核、內(nèi)存控制器等)、模塊之間如何互聯(lián)(總線結(jié)構(gòu))、以及如何進行功耗管理和時鐘分配。此時會搭建系統(tǒng)級模型進行初步驗證。

- 邏輯/電路設(shè)計:

- RTL設(shè)計:工程師使用硬件描述語言(HDL,如Verilog或VHDL),以代碼的形式描述芯片各模塊在寄存器傳輸級(RTL)的行為。這段代碼精確規(guī)定了數(shù)據(jù)如何在寄存器之間流動和處理,是設(shè)計的核心成果之一。

- 功能驗證:通過仿真工具,對RTL代碼進行大量的測試,確保其功能完全符合最初的設(shè)計規(guī)格。這一步會找出邏輯錯誤,是保證芯片“思想正確”的關(guān)鍵。

- 邏輯綜合:利用電子設(shè)計自動化(EDA)工具,將經(jīng)過驗證的RTL代碼,結(jié)合目標工藝庫(由芯片制造廠提供),自動轉(zhuǎn)換成門級網(wǎng)表。網(wǎng)表是由基本邏輯門(如與門、或門、非門)和觸發(fā)器構(gòu)成的電路連接圖,是邏輯電路的物理實現(xiàn)藍圖。

- 門級驗證與靜態(tài)時序分析(STA):對綜合后的門級網(wǎng)表再次進行功能驗證。進行STA,在不依賴仿真的情況下,通過計算分析所有路徑的時序,確保電路在指定的時鐘頻率下能夠可靠工作,沒有建立時間或保持時間的違規(guī)。

至此,芯片的“功能”和“邏輯”已完全確定,前端設(shè)計完成。

第二階段:后端設(shè)計——繪制芯片的“物理地圖”

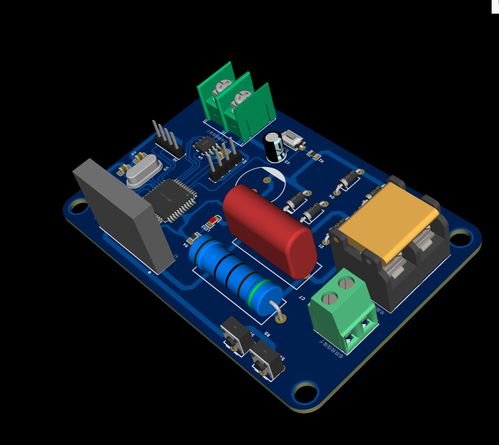

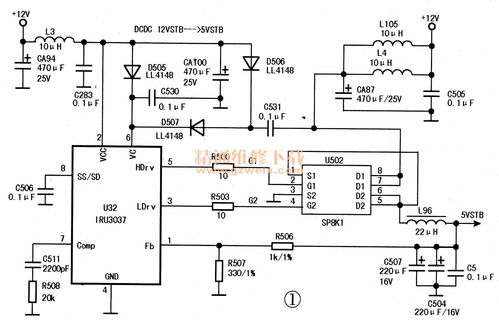

后端設(shè)計,也稱為物理設(shè)計,負責(zé)將門級網(wǎng)表轉(zhuǎn)換成制造用的光刻掩膜版圖,即芯片的“施工圖紙”。

- 布圖規(guī)劃:就像城市規(guī)劃,需要確定芯片核心面積、給各個功能模塊分配位置、規(guī)劃電源網(wǎng)絡(luò)和時鐘樹的走向。好的規(guī)劃能節(jié)省面積、提升性能、降低功耗。

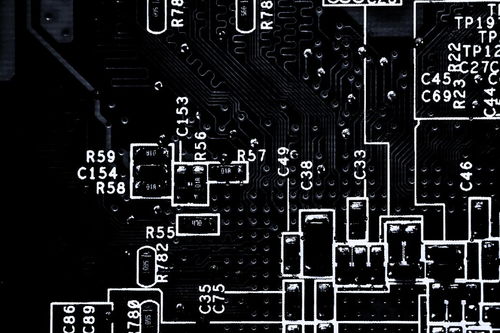

- 布局:將網(wǎng)表中的所有標準單元(邏輯門的物理實現(xiàn))和宏模塊(如內(nèi)存)精確地放置到芯片規(guī)劃好的區(qū)域內(nèi)。

- 時鐘樹綜合:構(gòu)建一個分布到所有時序單元的時鐘網(wǎng)絡(luò),目標是使時鐘信號盡可能同時到達所有端點,減少時鐘偏移,這對芯片高速穩(wěn)定運行至關(guān)重要。

- 布線:用金屬連線將布局好的所有單元按照邏輯關(guān)系連接起來。這需要在數(shù)十億計的連接中,避免短路、斷路,并滿足復(fù)雜的電氣和時序規(guī)則。布線是后端最復(fù)雜、最耗時的環(huán)節(jié)之一。

- 物理驗證與簽核:

- 設(shè)計規(guī)則檢查:確保版圖完全符合芯片制造廠制定的工藝設(shè)計規(guī)則,否則無法生產(chǎn)。

- 版圖與原理圖對比:確保物理版圖與原始邏輯網(wǎng)表在電氣連接上100%一致。

- 最終的時序與功耗分析:基于實際版圖的寄生參數(shù)(電阻、電容),進行更精確的STA和功耗分析,確保芯片性能達標。

所有驗證通過后,生成最終的數(shù)據(jù)格式(通常是GDSII文件),交付給芯片制造廠。這份“藍圖”將被用來制作一系列的光刻掩膜版,通過光刻、刻蝕、離子注入、薄膜沉積等數(shù)百道復(fù)雜工藝,在硅晶圓上刻畫出設(shè)計好的電路,經(jīng)過封裝測試,最終成為我們手中的芯片。

****

集成電路設(shè)計是一個高度依賴尖端EDA工具、嚴謹工程方法和跨學(xué)科知識的領(lǐng)域。前后端設(shè)計環(huán)環(huán)相扣,每一步都需經(jīng)過反復(fù)驗證,以確保這顆匯聚了數(shù)十億甚至上百億晶體管的復(fù)雜系統(tǒng)能夠一次成功。正是這一系列精密的設(shè)計流程,支撐著摩爾定律的持續(xù)推進,不斷將更強大、更智能的芯片帶入我們的生活。

如若轉(zhuǎn)載,請注明出處:http://www.yhbxs.com.cn/product/77.html

更新時間:2026-01-23 02:18:28